龙8国际头号玩家半导体元件制造涉及到一系列复杂的制作过程,将原材料转化为成品元件,以应用于提供各种关键控制和传感功能应用的需求。

半导体制造涉及一系列复杂的工艺过程,从而将原材料转化为最终的成品元件。半导体制造工艺通常包括四个主要阶段:晶片制造、晶片测试组装或封装以及最终测试。每个阶段都有其独特的攻坚点和机遇。

半导体制造工艺也面临着包括成本、复杂多样性和产量在内的诸多挑战,但也为创新和发展带来了巨大的机遇。通过应对其中的困难并抓住机遇,推进研发新技术来改变我们的生活和工作方式,同时促使行业可以持续发展和壮大。

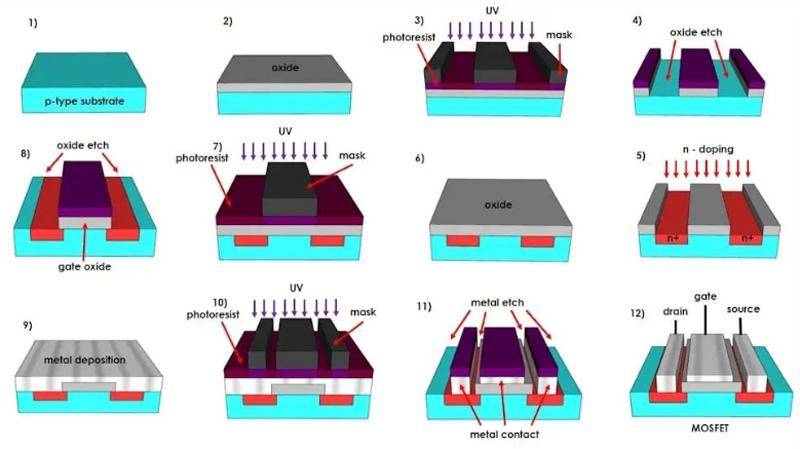

在这一过程中,使用称为光刻的工艺在硅晶片上创建图案。将一层抗腐蚀的光刻胶施加到晶片表面,然后将掩模放置在晶片顶部。掩模上具有对应的相关预制造的电子元件的图案。然后使用紫外光将图案从掩模转移到光刻胶层上。曝光的光刻胶区域随后被去除,最终在晶片上留下图案化的表面。

在这个步骤中,材质被添加到硅晶片中以改变其电特性。最常用的材质是硼或磷,少量加入可以分别产生p型或n型的半导体。这些材质是通过一种称为离子注入的工艺,利用离子加速,将被加速的离子注入到晶片的表面。

在这个制作过程中,薄膜材料被沉积在晶片上以生成电子元件。这可以通过多种技术来实现,包括化学气相沉积(CVD)、物理气相沉积(PVD)和原子层沉积(ALD)。这些工艺可用于沉积金属、氧化物和氮化物等材料。

从晶片表面去除部分材质龙8头号玩家,以产生电子元件所需的形状和结构。可以使用多种技术来进行蚀刻,包括湿式蚀刻、干式蚀刻和等离子蚀刻。这些工艺使用化学物质或等离子体从晶片上选择性地去除特定的材质。

电子元件被封装成可用于电子设备的最终产品。这包括将元件连接到诸如印刷电路板的基板上,然后使用导线或其他方式将它们连接到其他元件上。半导体工艺非常复杂,涉及各种专用设备和材料。这些工艺对于现代电子设备的制造是必不可少的,并且随着新技术的迭代而不断发展。

通常,生产半导体芯片的过程需要几周到几个月的时间。从第一阶段开始,需要制造一个硅片,作为芯片的衬底。此工艺通常包括如下过程,清洗、沉积、光刻、蚀刻和掺质。晶片可能需要经受数百个不同的工艺加工,所以,整个晶片制造过程可能要花费长达16~18周的时间。

当在晶圆上制造出独立的单一芯片,就需要将它们分离并封装成独立的单元。同时包括测试每个芯片以确保其符合规格要求,然后将其从晶圆上分离并安装到封装或基板上。芯片封装后,会经过严格的测试过程,以确保它们符合质量标准并达到预期的功能。这包括运行电子测试、功能测试和其他类型的验证测试,以识别任何缺陷或问题。这也取决于芯片的复杂程度和所需的测试要求,所以这一封装和测试过程可能需要8-10周的时间。

总而言之龙8头号玩家,生产半导体芯片的整个过程可能需要几周或几个月的时间,其因是它取决于所使用的相关技术和芯片的设计复杂程度。

图案转移技术的进步已经成为半导体工业快速发展的关键驱动力,进而能够制造更小和更复杂的电子元件。

图案转移技术的一个主要进步是先进光刻技术的发展,光刻是使用光或其他辐射源将图案转移到媒质面上的过程。尤其近几年开发的光刻技术,例如极紫外(EUV)光刻和多重图案化技术,用以产生更小和更复杂的图形。

EUV平版印刷术使用极短波长的光束在硅晶片上制作极其精密的图形,这种技术能够创造微小到几纳米的尺寸,这对于制造微处理器等先进电子元件至关重要。

多重图案化是另一种光刻技术,它能够制作更小的图案。此技术包括将单个图案分解成多个微量极的图案,然后转移到晶片表面。致使创建的图案可以小于光刻技术中所使用的辐射波长。

掺质是向硅片中加入特定的介质以改变其电特性,掺质技术的进步一直是半导体行业快速发展的关键因素。这一技术的进步是得益于新的介质材料的出现。

传统上,硼和磷是最常用的掺质材料,因为它们可以分别产生p型和n型半导体。然而,近年来,锗、砷和锑等新材料已被开发出来,可用于制造更复杂的电子元件。

掺质技术的另一个进步是更精确的掺质工艺的进步。在过去,离子注入是用于掺质的主要技术,包括高速离子的运用,将介质注入晶片的表面。虽然离子注入仍然被普遍使用,但是诸如分子束外延(MBE)和化学气相沉积(CVD)等新技术已经被开发出来,使掺质处理过程得到更精确的控制。

沉积是半导体制造中的又一关键工艺,包括将材料薄膜沉积到衬底上。这一过程可以通过各种技术实现,例如物理气相沉积(PVD)、化学气相沉积(CVD)、原子层沉积(ALD)等。

同时,新技术也在不断的发展,包括金属有机化学气相沉积(MOCVD)、等离子体增强沉积、卷对卷沉积等。

蚀刻包括去除半导体材料的特定部分以产生图案或结构。蚀刻技术的进步是半导体工业快速发展的主因,也是制造更小和更复杂的电子元件的关键技术。

过去,湿法蚀刻是普遍应用的主要技术,包括将晶片浸入溶解材料的溶液中。然而,湿法蚀刻并不精确,会对相邻结构造成损伤。

干法蚀刻技术的出现,实现了更精确和高可控的蚀刻制作,诸如反应离子蚀刻(RIE)和等离子体蚀刻。RIE是一种使用反应离子体从晶片上选择性去除材料的技术,允许对蚀刻过程进行精确控制。

而等离子体蚀刻是一种类似的技术,使用气体等离子体来去除材料,但是它具有选择性地去除特定材料的额外好处,例如金属或硅。

半导体制造中的封装工艺包括将集成电路封装在保护外壳中,该保护外壳还提供与外界的电连接。封装过程会影响最终产品的性能、可靠性和成本。

3D封装包括将多个芯片堆叠在一起,以创建高密度集成电路。这种技术可以减小器件的整体尺寸并提高其性能,同时还能降低功耗。

扇出(fan-out)封装是一种将集成电路嵌入环氧模塑料层的技术,使用从芯片扇出的铜柱进行电连接。这项技术能够以更小的尺寸实现高密度封装。

系统级封装(SiP)是另一种将多个芯片、传感器和其他组件集成到一个封装的技术。它可以做到减小器件的整体尺寸,同时还能提高其综合性能。

最后,毛遂自荐一下,小猫芯城成立于2015年,一站式电子元器件采购商城,提供1000万+种电子元器件,聚惠百万品牌好货,100%原装正品,闪电发货,让元器件采购更简单!返回搜狐,查看更多